Eletrônica Digital: Flip - Flops:

1. Introdução:

Em um latch D ativado por um sinal de clock alto, existem alguns problemas que podem ocorrer em um sistema eletrônico. A medida que os sinais de D vão variando, muitas vezes os sinais de saída Q e Q’ podem se alterar, em um curto espaço de tempo, antes atpe mesmo de uma estabilização de sinais.

Em muitos projetos, essa característica do Latch pode ser inviável, por isso, os flip-flops podem ser uma forma de circuito de memória mais estável e mais aplicavel em determinada situações.

2. Flip-Flop D:

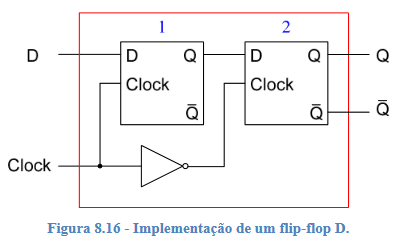

Um Flip-Flop D é um dispositivo de memória, no qual e formado por dois Latchs D.

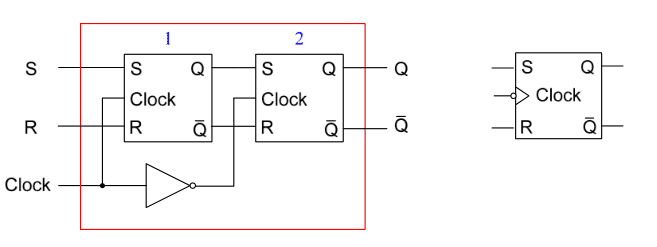

Em primeiro, vamos analisar um circuito de implementação de um Flip-Flop D:

Veja que quando o sinal do clock (clk) estiver em nível alto, o bloco 1 está ativado, por outro lado o bloco 2 está desativado, pois observe a porta inversora no clock a caminho do bloco 2. Assim que o clock sai do sinal 1 e vai para 0, o latch 1 fica desativado e o latch 2 ativa.

Conclui-se que no instante imediato de mudança de sinal do clk = 1 para clk = 0, o latch 2 será ativado, recebendo o sinal do latch 1 (anteriormente ativado – agora desativado), podendo ter uma provavel mudança de sinal de saída Q.

Ressalta-se que o Flip-Flop D descrito acima, somente irá caputrar as informações efetivamente quando o sinal do clock estiver na mudança de alto para baixo. (Podemos identificar como “Edge negativo do clock/ descida do clock”).

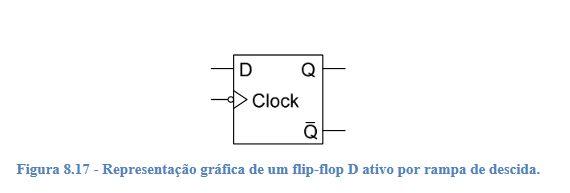

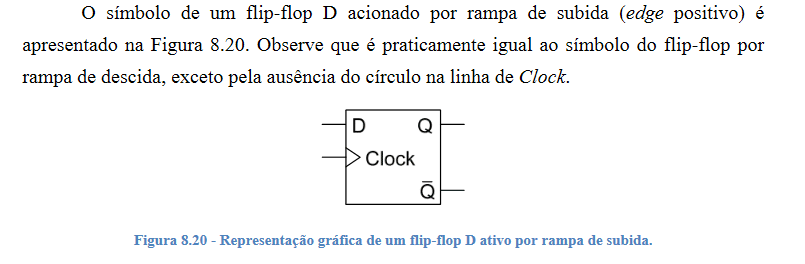

Podemos representar esse tipo de flip-flop nessa forma de diagrama:

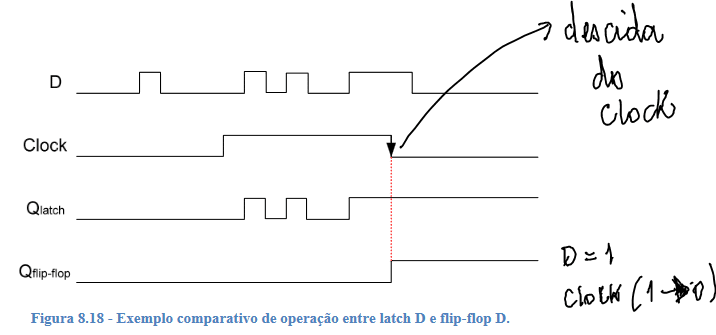

O diagrama de sinais em função do tempo fica dessa forma:

A próxima possível mudança somente ocorrerá, na descida subsequente do clock, ou seja de 1 -> 0.

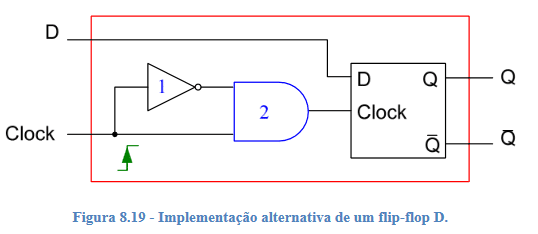

Alguns fabricantes, utilizam, produzem flip-flops D ativados na subida da curva, o que torna um pouco diferente. Veja a implementação empregada:

Então contrário ao flip-flop D ativado pelo edge-negativo, esse flip-flop só tem condições de alterar seu sinal de saída, se, e somente, se o clock estiver em rampa de subida, ou seja,instante do clock de sinal de 0 para 1.

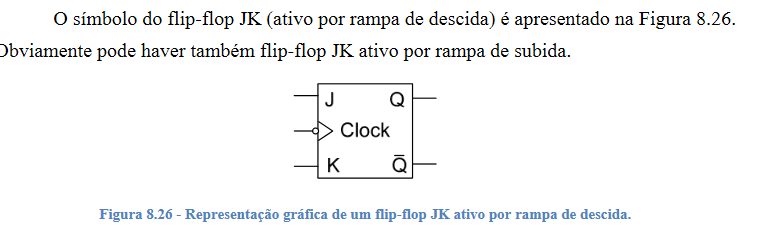

3. Flip-Flops J-K:

Os Flip-Flops J-K lembram muito a implementação de dois latches S-R (set-reset). Ou seja, além da entrada do sinal de clock, temos a entrada de J e K, no qual temos o total de 3 entradas de sinais. Sendo assim:

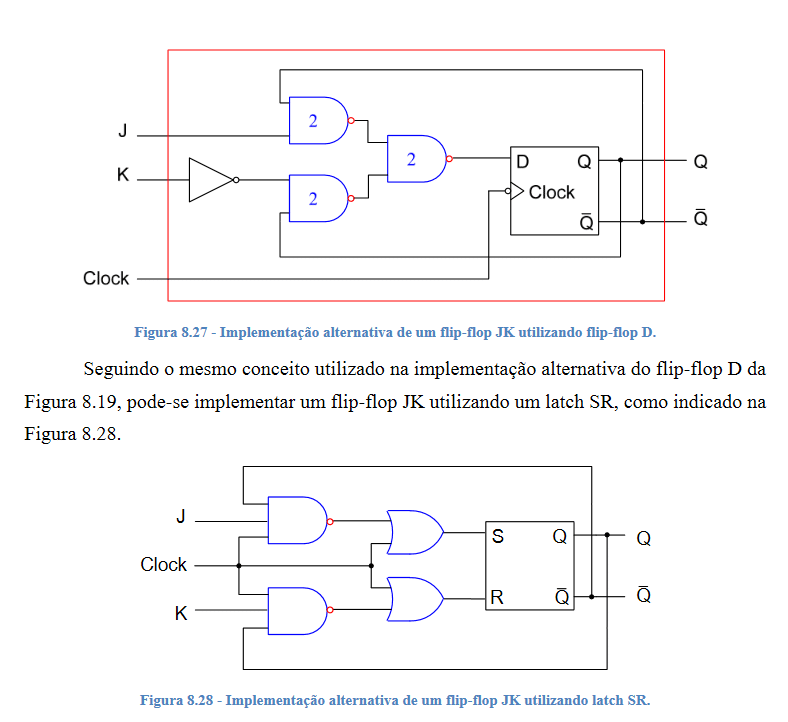

Considerando um flip flop S-R ou seja, uma juntada de dois latches S-R, temos um engatilhamento de tal circuito na rampa de descida do sinal do clock. O grande problema desses circuitos são a situação proibitiva no qual pode ocorrer, tal situação é descrita com S = 1 e R =1, fazendo com que esse dispositivo de memória não seja tenha a função requerida. Para evitar esse tipo de disfunção, foi criado o Flip-Flop J-K.

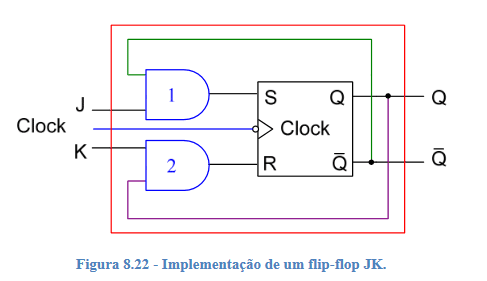

O circuito de implementação do Flip-Flop J-K é descrito da seguinte forma:

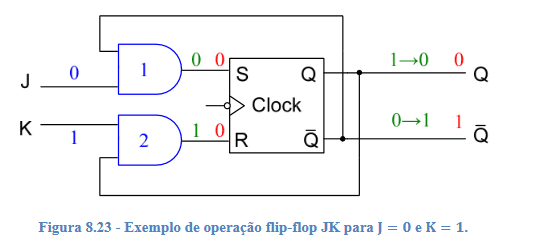

- Vamos considerar algumas situações para o melhor entendimento da operação do Flip-Flop J-K: Como condição inicial, temos Q , J=0 e K=1:

a) Considerando inicialmente Q(t)=1, pela realimentação da condição inicial, temos as seguintes operações:

- (Q.K) = R ; Na porta 1.

- (Q’.J) = S ; Na porta 2.

No caso temos que Q=1 e K=1 então: R = (1.1) = 1

Já no caso em que J =0, já é o suficiente para constatar que: S = (0.Q’) = 0.

Portanto temos uma mudança de estado de Q(t) = 1 para Q(t+1) = 0, onde Q(t) é a condição inicial proposta.

Assim como Q'(t) = 0 para Q'(t+1) = 1.

b) Considerando, como estado inicial Q(t) = 0, pela realimentação, temos as seguintes operações:

- R = Q(t).K , já que Q(t) = 0 então já temos que R =0.

- S = Q'(t).J, já que temos J =0, temos que S =0.

Portanto sabendo que S = 0 e R =0, do próprio funcionamento dos latches S-R, o circuito mantém o estado de saída, que no caso é Q(t+1)=0, onde Q(t) é o estado anterior dado por 0 na inciso b.

Assim como Q'(t) = 1 e Q'(t+1) = 1.

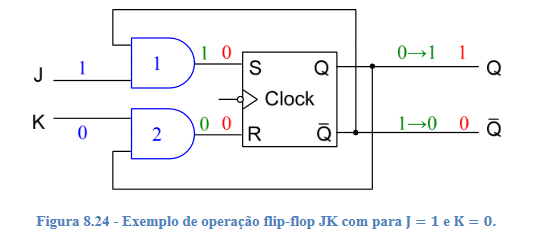

2) Considerando J = 1 e K = 0 e um estado inicial Q(t).

a) Considerando Q(t) = 1, pela realimentação temos:

R = 0, independente de Q(t), pela condição constatada pela porta E.

Já que Q(t) = 1, então Q'(t) = 0, então com esse valor, sabemos que S= 0 também.

Portanto da mesma forma que anteriormente, o sinal de saída Q(t+1) e Q'(t+1) será o mesmo valor que Q(t) e Q'(t). Manuntenção de estado.

Nesse caso: Q(t+1) = 1 e Q'(t+1) = 0.

b) Considerando Q(t) = 0, pela realimentação temos:

R = 0, independente de Q(t), pela condição constatada pela porta E.

Já que Q(t) = 0, então Q'(t) = 1, então temos:

S = (Q'(t).J) = (1.1) = 1. Tornando os valores de S = 1 e R = 0, então Q(t+1) =1 e Q'(t+1) = 0.

Portanto há uma mudança de estado de Q(t) = 0 -> Q(t+1) = 1.

3) Considerando J=K=0, facilmente é visivel que tanto S=0 como R=0, mantendo o estado anterior Q(t).

Portanto Q(t+1) = Q(t) e Q'(t+1) = Q'(t).

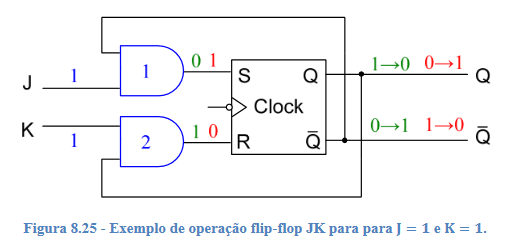

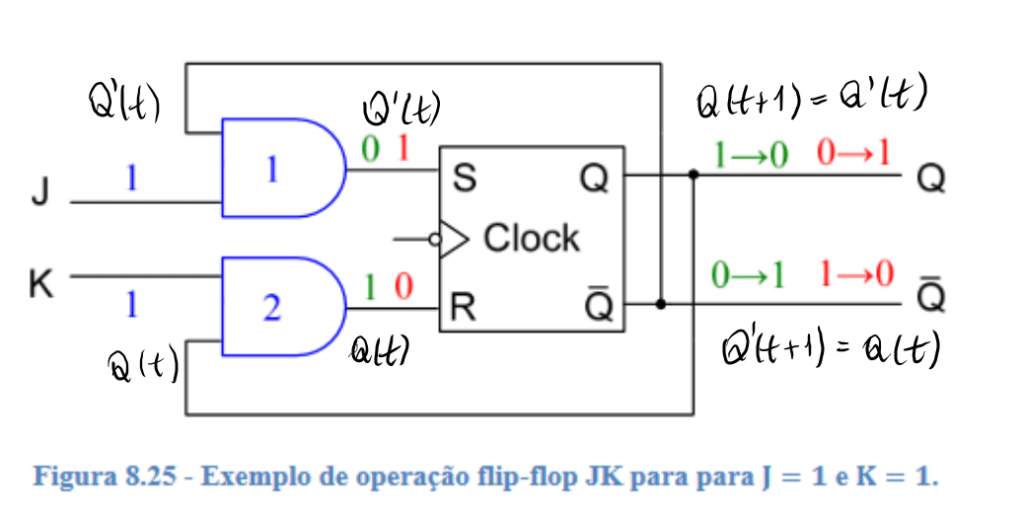

4) Considerando o estado Inicial Q(t) e J=K=1, temos:

Com essas condições, temos as seguinte situação descrita abaixo:

Veja que independente do valor de Q(t) inicial, com J=K=1 temos a mudança de estado.

Caso Q(t) = 1, então Q(t+1) = 0.

Caso Q(t) = 0, então Q(t+1) = 1.

REFERÊNCIAS:

- PIMENTA: Circuitos Digitais – Análise e Síntese Lógica: Aplicações em FPGA. Editora Elsevier (2018);

2. BROWN: Fundamental of Digital Logic with Design in VHDL. 2 Edition (2010) .