Eletrônica Digital: Latch Assíncrono (Parte I)

1) Introdução:

Existem duas grandes classificações para circuitos lógicos no estudo da eletrônica digital. Há os circuitos combinacionais e os circuitos sequênciais. No caso dos Latches, e outros conteúdos que vamos ver futuramente como flip-flops e registradores são baseados nos circuitos sequênciais.

A diferença entre ambos os circuitos são dado pelo valor de saída dos circuitos. O circuito combinacional tem como valor de saída em função somente dos valores de entrada (input), já o sequenciais dependem dos valores de entrada e o estado no qual o circuito se encontra.

O estado de um circuito depende dos elementos armazenados em um instante anterior a qualquer mudança de valor de entrada. Com as mudanças de entrada em conjunto com o estado que o circuito sequencial está, podemos determinar se esse circuito irá mudar de estado no próximo instante ou não.

Uma vez que estamos falando de valores armazenados e a função do tempo (instantes) em um circuito lógico, podemos afirmar que os Laches, Flip-Flops e Registradores são circuitos de memória.

Esses dispositivos básicos de memória podem ser usados como aplicação tanto em contadores como em grandes processadores utilizados no dia a dia.

2) Exemplo de um Alarme em uma loja:

Antes de entrarmos diretamente no assunto de circuitos sequenciais, vamos dar um exemplo na pratica do dia a dia. Vamos considerar um alarme, no qual possui dois estados: Ligado (Disparado) ou Desligado.

Podemos dizer que o alarme responde a duas entradas chamadas de On (Ligado) ou Off(Desligado), pensando de forma racional, o alarme só irá disparar se a entrada ON = 1 e OFF = 0. E o alarme estará desligado somente se ON = 0 e OFF = 1. Podemos fazer uma pequena alteração nas entradas de modo: ON/OFF ‘= 1 (OFF ‘ = OFF NEGADO) para o alarme ligado e ON/OFF ‘ = 0 alarme desligado.

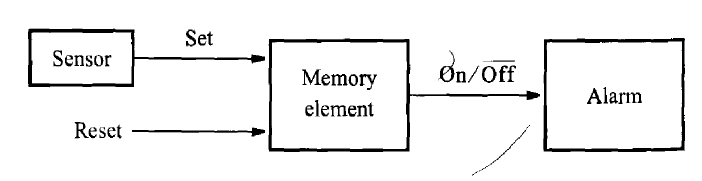

Um circuito básico para isso seria mais ou menos assim:

Chamamos de set o valor de entrada que irá ativar o alarme e o reset o valor que irá desligar o alarme. Porém esse exemplo nos diz muito sobre o estado que o alarme está, pense comigo, não tem como desligar o alarme que já está desligado e não tem como ativar o alarme quando o alarme já está ativado. Então precisamos levar em conta além da entrada, mas o estado em que o alarme está nesse instante, o sinal de reset só irá mudar o estado do alarme se ele estiver ligado, e o mesmo dizemos, que o alarme só irá disparar se ele estiver no estado desligado.

3) Latch Assíncrono (Utilizando o circuito Não - ou):

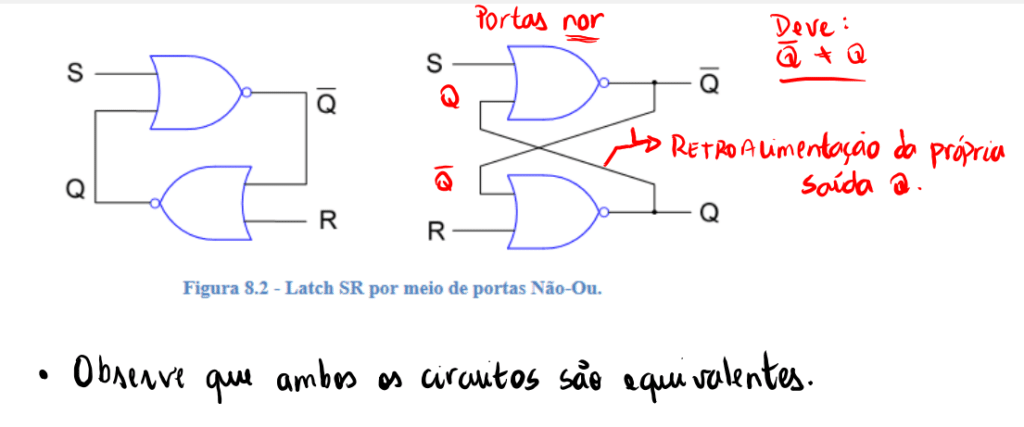

Vamos inicialmente falar sobre o Latche ser assíncrono, ou seja, somente há entradas de sinais a partir do set e do reset. A característica de não síncrono deve-se a não ter uma variável de controle na entrada do circuito, assim conhecido como o clock.

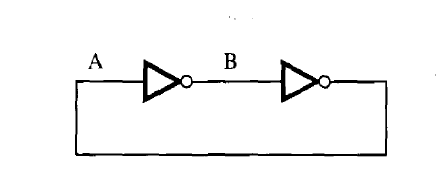

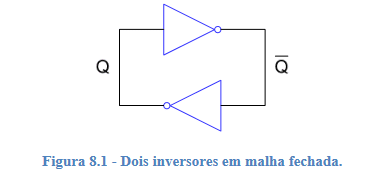

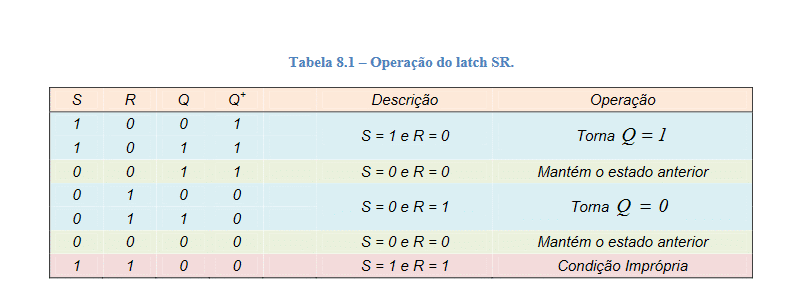

Um tipo espercífico de Latch SR – Latch Set-Reset – tem duas entradas já ditas anteriormente: Set e o Reset e duas saídas Q e Q’ (Q negado), O sinal de saída Q representa o estado que o circuito sequencial está. Veja que as saídas Q e Q’ DEVEM TER VALORES OPOSTOS, ou seja, quando Q = 0, Q ‘ = 1 ou Q = 1 , Q’ = 0. Portanto é necessário ter um circuito no qual satifaz essa condição lógica entre Q e Q ‘.

Como Exemplo temos: (Lembre-se que Q barra é igual a Q’ ).

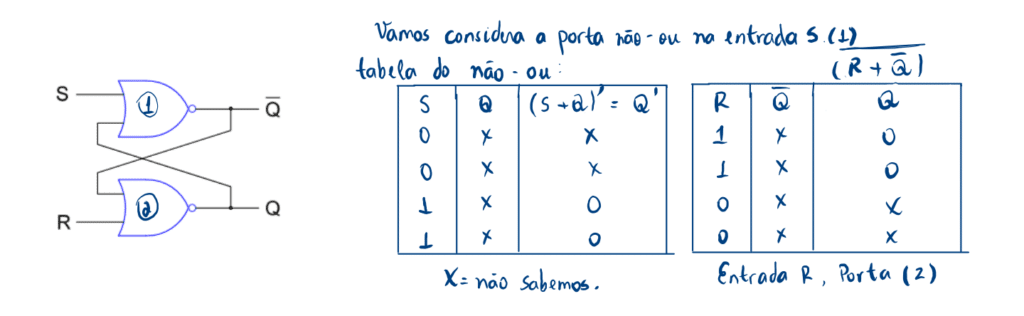

Agora vamos considerar a retro-alimentação do circuito, uma vez que além do circuito depender das entradas, o circuito sequencial deve depender saída que no caso é o estado no qual o latch se encontra. É necessário portanto, um circuito lógico no qual a saída de Q no instante “atual” dependa dos valores de entrada e do próprio valor de saída no instante anterior. Um exemplo de circuito que satisfaça tais condições é dado por:

Interpretação sobre o circuito Latch SR da figura 8.2:

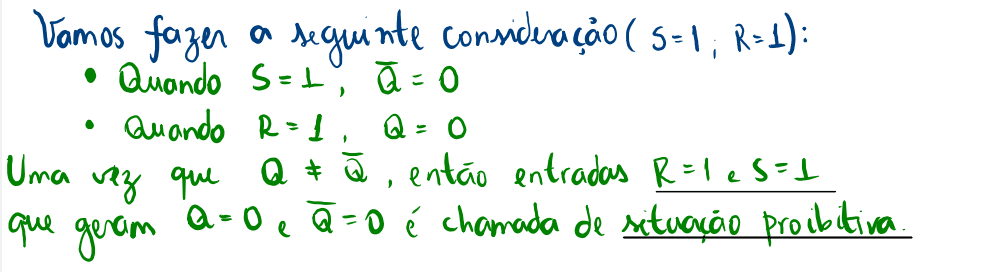

A) Caso S=1 e R=1:

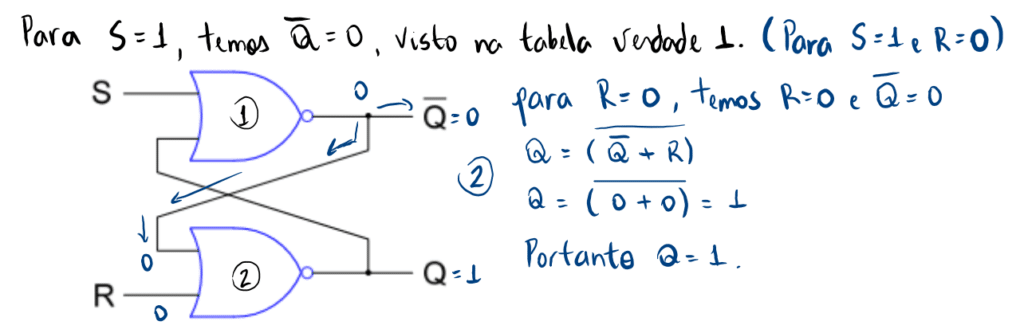

B) Caso S=1 e R=0:

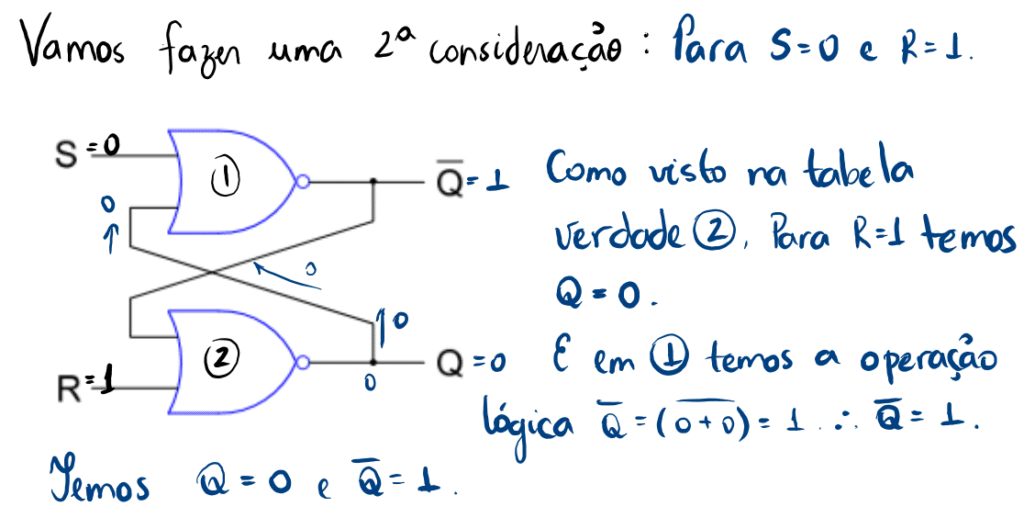

C) Caso S=0 e R=1:

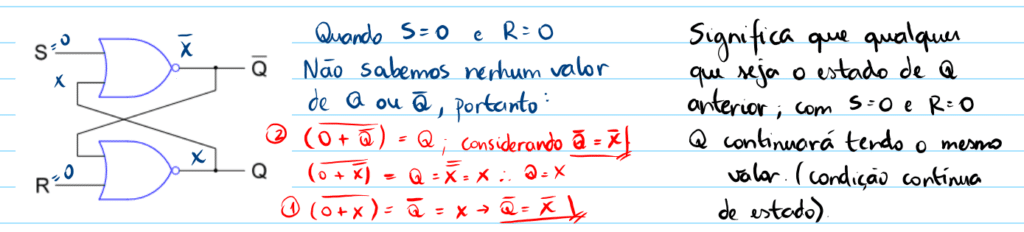

D) Caso S=0 e R=0:

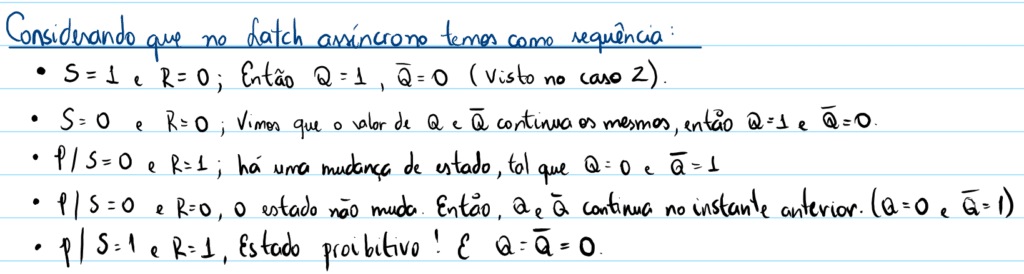

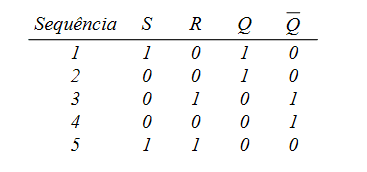

4) Interpretação da Sequência do Latch assíncrono:

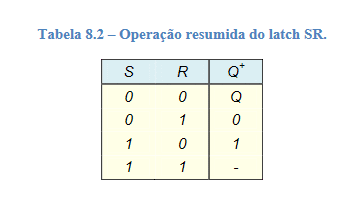

RESUMO:

REFERÊNCIAS:

- PIMENTA: Circuitos Digitais – Análise e Síntese Lógica: Aplicações em FPGA. Editora Elsevier (2018);

2. BROWN: Fundamental of Digital Logic with Design in VHDL. 2 Edition (2010) .